# Architecture Languages and Integrated Analysis

#### Systems Engineering BSc Course

Budapest University of Technology and Economics Department of Measurement and Information Systems

# Platform-based systems design

# Learning Objectives

## Function-platform allocation

- •Summary of extra-functional system properties

- •Brief overview of platform modeling in SysML

- •Describe allocation specification in the SysML language

### **Case-studies**

- See approaches to capture allocation information on models from different domains

- Analyze extra-functional properties of the integrated allocation model

ADLs

# **Architecture Description Languages**

# Abstract

- "The architecture of a program or computing system is the structure or structures of the system, which comprise software components, the externally visible properties of those components, and the relationships among them."

- (no universal agreement on what ADLs should represent)

Software Architecture in Practice, Bass, Clements, and Kazman

# Architecture Analysis and Design Language (AADL)

## AADL

- Architecture Analysis and Design Language (AADL) is a standard architecture modeling language

- Avionics

- Aerospace

- Automotive

- Robotics

- Component based notation

- Task and communication architecture

- Designed for modeling and analysis in mind

- SAE standard (AS 5506A)

- First was called Avionics Architecture Description Language

O Derived from MetaH created by Honeywell

- V1 version in 2004

- V2 version in 2009

# AADL

- Based on the component-connector paradigm

- Key Elements:

- Core AADL language standard (V2-Jan, 2009, V1-Nov 2004)

Textual & graphical, precise semantics, extensile

- AADL Meta model & XMI/XML standard

Model interchange & tool interoperability

- Annexes Error Model Annex as standardized extension

- Error Model Annex addresses fault/reliability modeling, hazard analysis

- UML 2.0 profile for AADL

- Transition path for UML practitioner community via MARTE

- EMF representation also available (without EFeatureMap!)

# AADL

- Precise execution semantics for components

- Thread, process, data, subprogram, system, processor, memory, bus, device, virtual processor, virtual bus

- Continuous control & event response processing

- Data and event flow, synchronous call/return, shared access

- End-to-End flow specifications

- Operational modes & fault tolerant configurations

Modes & mode transition

- Modeling of large-scale systems

- Component variants, layered system modeling, packaging, abstract, prototype, parameterized templates, arrays of components and connection patterns

- Accommodation of diverse analysis needs

- Extension mechanism, standardized extensions

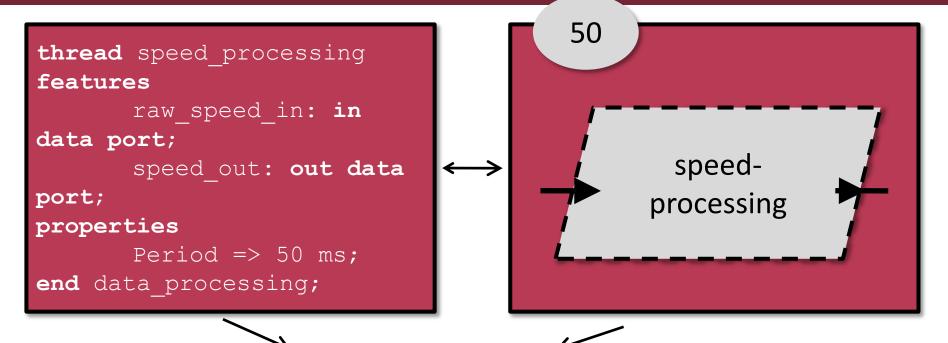

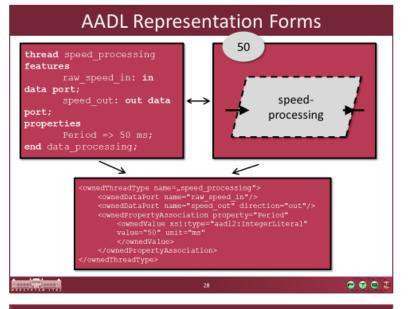

### **AADL** Representation Forms

<ownedThreadType name="speed\_processing">

<ownedDataPort name="raw\_speed\_in"/>

<ownedDataPort name="speed\_out" direction="out"/>

<ownedPropertyAssociation property="Period"

<ownedValue xsi:type="aadl2:IntegerLiteral"

value="50" unit="ms"

</ownedValue>

</ownedPropertyAssociation>

</ownedThreadType>

# **AADL** Language Elements

- Core modeling

- Components

- Interactions

- Properties

- Engineering support

- Abstractions

- Organization

- Extensions

- Infrastructure

- Strong modeling capabilities for embedded SW and Computer systems

# **AADL** Components

Top element system Example: package F22Package public system F22System end F22System; system WeaponSystem end WeaponSystem; system implementation F22System.impl subcomponents weapon: **system** WeaponSystem; end F22System.impl; end F22Package;

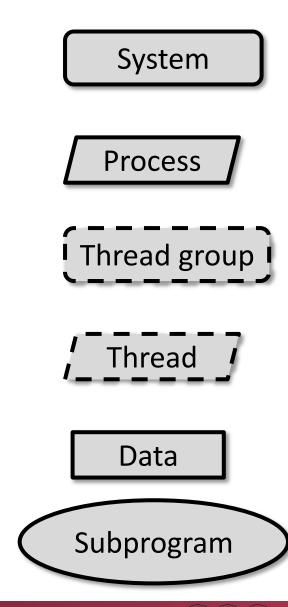

# AADL SW Components

- System hierarchical organization of components

- Process protected address space

- Thread group logical organization of threads

- Thread a schedulable unit of concurrent execution

- Data potentially sharable data

- Subprogram callable unit of sequential code

RG

## AADL SW Components

### Process

- Protected virtual address space

- Contains executable program and data

- Must contain 1 thread

### Thread

- Concurrent tasks

- Periodic, aperiodic, sporadic ,background, etc.

- Interaction through port connection, subprogram calls or shared data access

- errors: recoverable, unrecoverable

# AADL SW Components

### Ports and Connections

- Data (non queued data), Event (queued signals) or Event data (queued messages)

- Complex Connection hierarchies through components

- Timing

- Feature groups

- Data

- Optional but makes the analysis more precise

### Flows

Logical flow of data and control

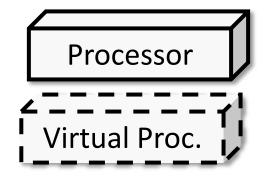

# **AADL** Computer Components

- Processor / Virtual Processor –

Provides thread scheduling and

- Memory provides storage for data and source code

- Bus / Virtual Bus provides physical/logical connectivity between

- Device interface to external environment

## AADL Computer Components

- "Real" HW components

- Bus transmission time, latency,

- Processor timing, jitter

- Memory capacity

- o Etc.

- Logical resources

- Thread scheduling of a processor

- Communication protocol overt network connection (modeled as bus)

- Transactional memory (modeled as memory)

## **AADL Computer Components**

#### Processor

- o As HW

- MIPS rating, size, weight, clock, memory manager

- As Logical resource

- Schedule threads → scheduling policies and interruption

- Execute SW

#### Bus

- o As HW

- Physical connection inside/between HW components

- As logical resource

- Protocol, which are used for the communication

#### Memory

- Processes must be in memory

- Processors need access to memory

#### Device Components

- Represents element that are not decomposed further

- Sensors/Actuators

- Device Driver

# AADL Binding

### Binding

- Bringing SW models and the execution platform together

- Virtual processors → can be subcomponents of other virtual processors → ARINC653 partitioning

- Hierarchical Scheduling

- Virtual buses to physical ones

- One-to-one

- Many-to-one

# Summary

- After 15 years of mainly DoD research it is getting mature enough

- Many pilot project uses AADL

- o FAA

- o DoD

- Lockheed Martin

- Rockwell Collins (Steven P. Miller)

- Many research paper on formal analysis, simulation and code generation

- Ongoing harmonization with SysML and MARTE

# History

- AUTomotive Open System ARchitecture

- Started in 2002

- BMW, Bosch, Daimler, Conti, VW, + Siemens

- Industrial standardization group

- Current standard version: 4.0 (end 2009)

- Currently we use 3.1 (end 2008)

- Members: OEMs, Tool vendors, Semiconductor manufacturers I Europedominated

- Scope

- Modeling and implementation of automotive systems

- Distributed

- Real-time operating system

- $\circ~$  String based interaction with HW and environment

- Out of scope

- GUI, Java, internet connectivity, File systems, Entertainment systems, USB connectivity etc.

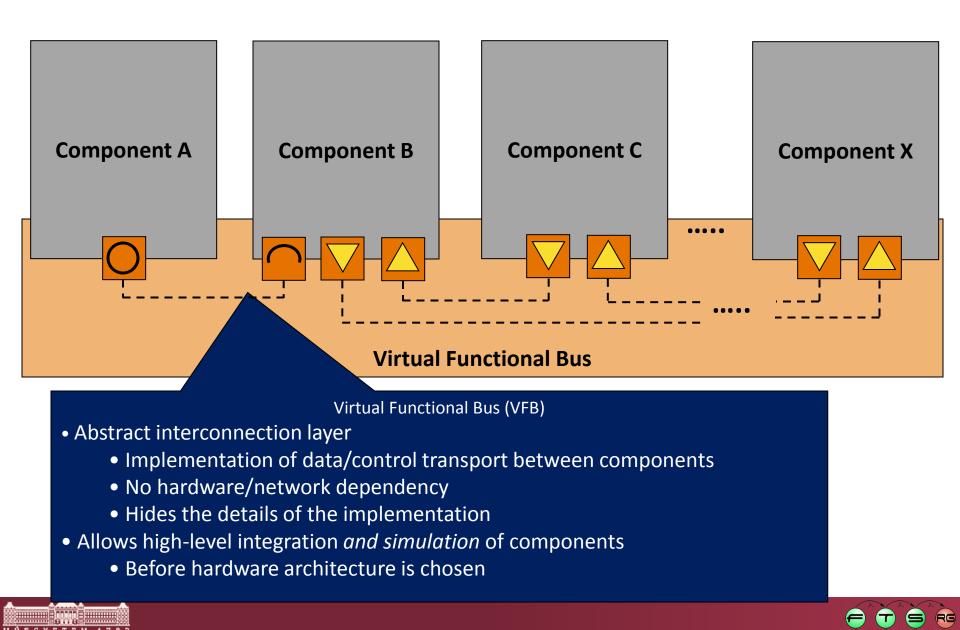

# Key Concepts of AutoSAR

- A standard runtime architecture

- component-oriented

- layered

- o extensible

- New functionalities

- New components (component implementations)

- all major interfaces standardized

- Standardized Run Time Environment (RTE)

- A standard modeling and model interchange approach

- follows the principles of model-driven design

- supports the interchange of designs

- $\circ\;$  supports the collaborative development

- Between different developers,

- Teams,

- And even companies

- Conformance test framework

- assuring the conformance to the standard

- Still evolving new in version 4.0

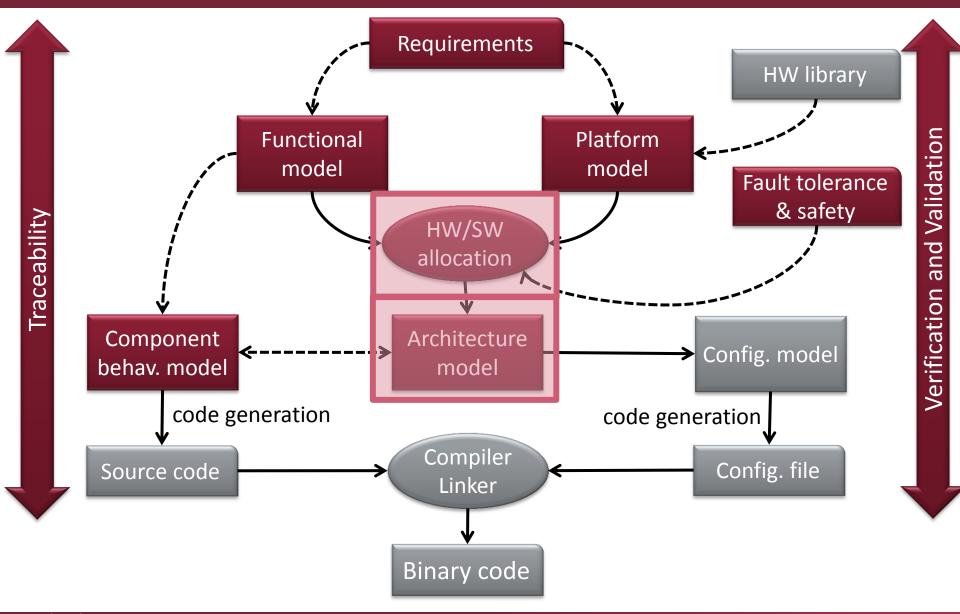

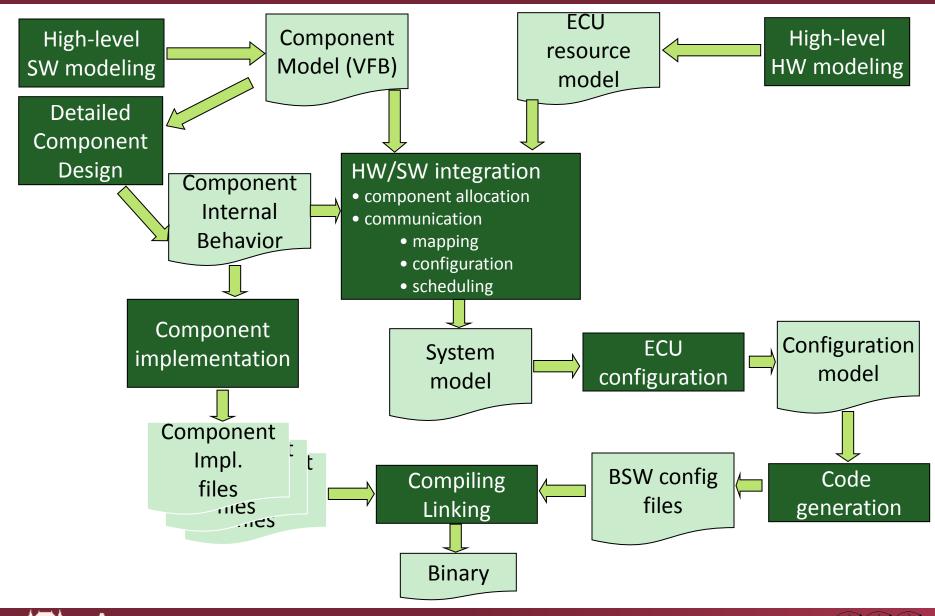

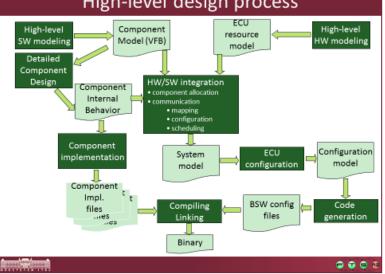

### **High-level design flow**

• Non-AR: behavioral models/design

MÚEO

GYETEM

MÚEGYETEM

RG

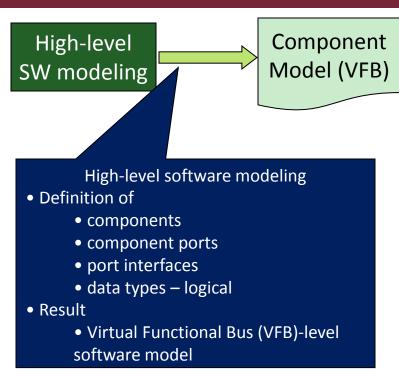

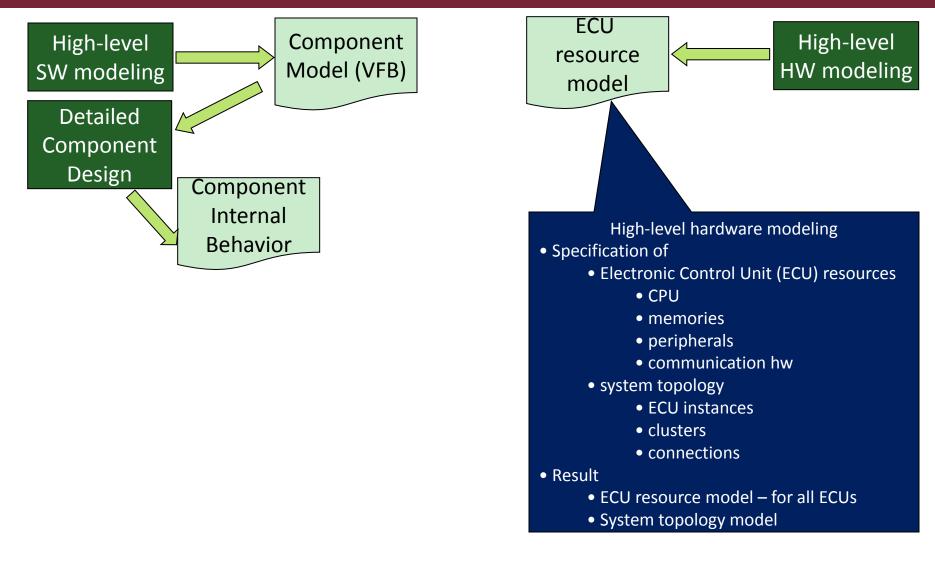

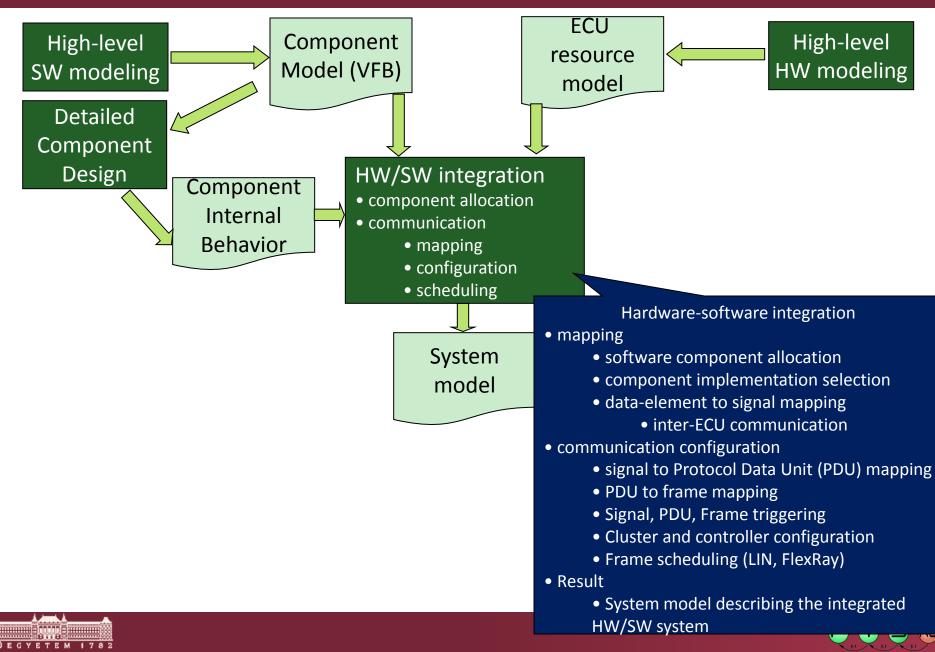

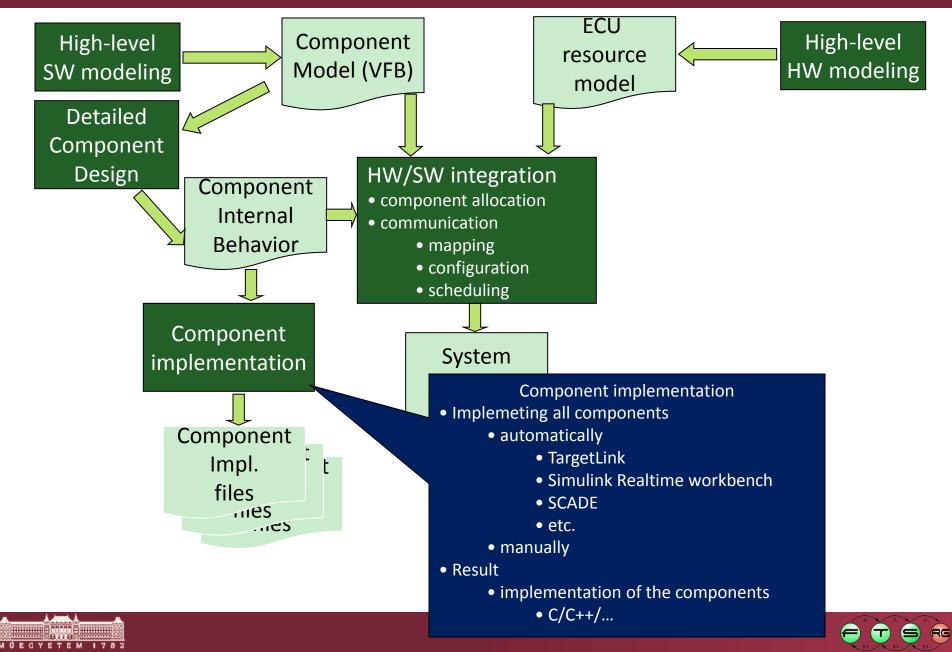

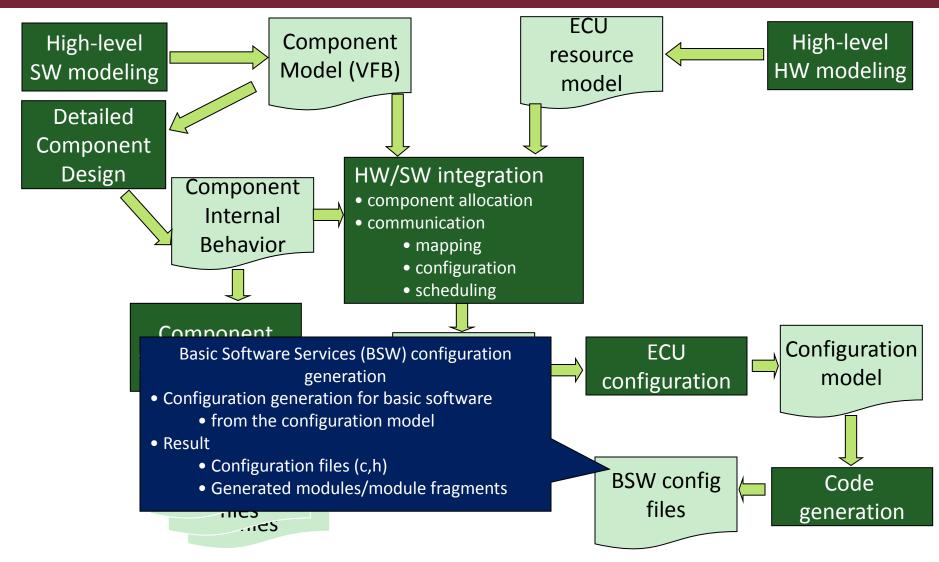

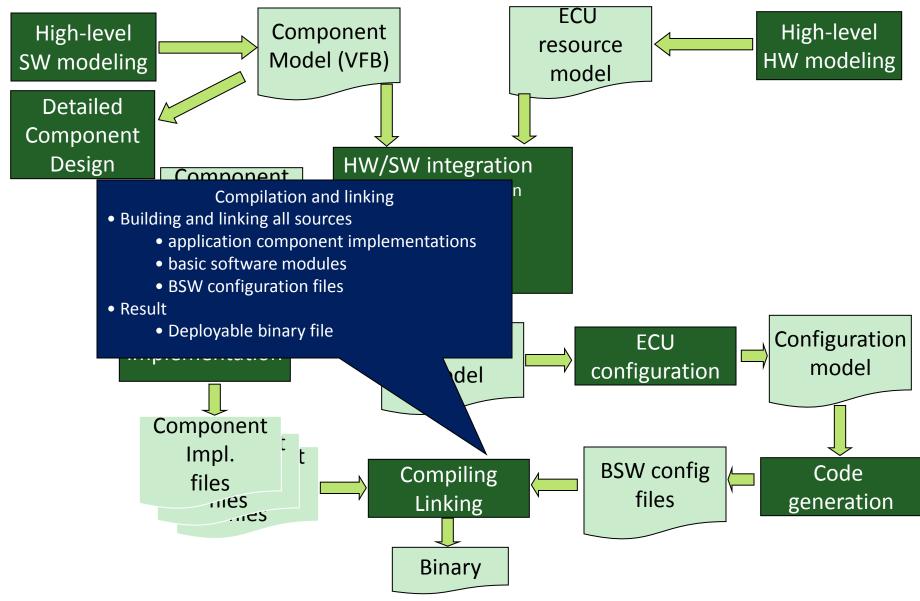

# Models in the design flow

- Software Component Template

- Components, ports, interfaces

- Internal behavior

- Implementation (files, resource consumption, run time, etc.)

- ECU Resource Template

- Hardware components, interconnections

- System Template

- System topology, HW/SW mapping

- o Comm. matrix

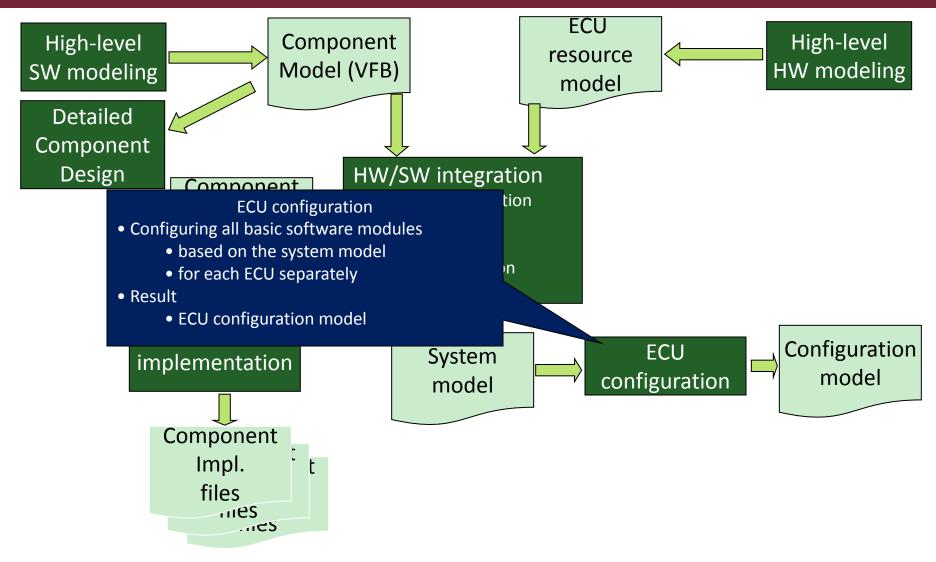

# Models in the design flow 2

- Basic Software Module Template

- BSW modules

- Services

- Schedulable entities

- Resource consumption

- ECU Configuration Parameter Definition Template

- Configurable parameters of BSW modules

- ECU Configuration Description Template

- Actual configurations of BSW modules

- Based on the ECU Parameter Definition

# AUTOSAR vs. UML/SysML/... modeling

- AUTOSAR defines models with

- Domain Specific Constructs

- *Precise* syntax

- Synthesizable constructs

- Direct model -> transformations

- Direct model -> detailed model mappings

- Different abstraction levels

- From Virtual Function Bus to configuration

- Result

- Models *are* primary design *and* implementation artifacts

- More precise, consistent modeling should be done

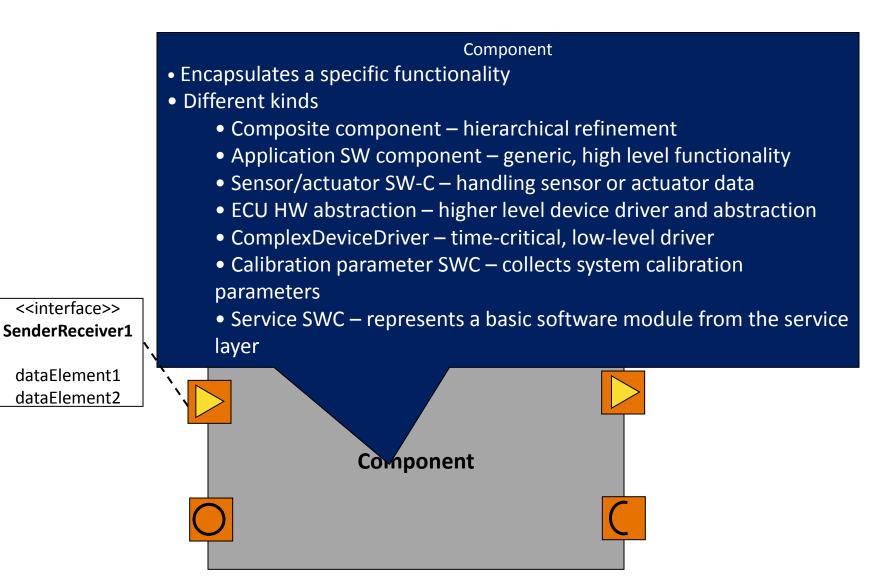

#### **AUTOSAR Components**

### **Component-oriented design**

#### What is a component?

- "A component is a self contained, reusable entity that encapsulates a specific functionality (and/or data), and communicates with other components via explicitly defined interfaces."

- AUTOSAR uses the term *component* for application-level components

- Elements related to the high-level functionality of the system under design

- Basic software (middleware) components are called modules.

- Standard elements of the AUTOSAR architecture

#### **Component-based** approach

#### **Component-based** approach

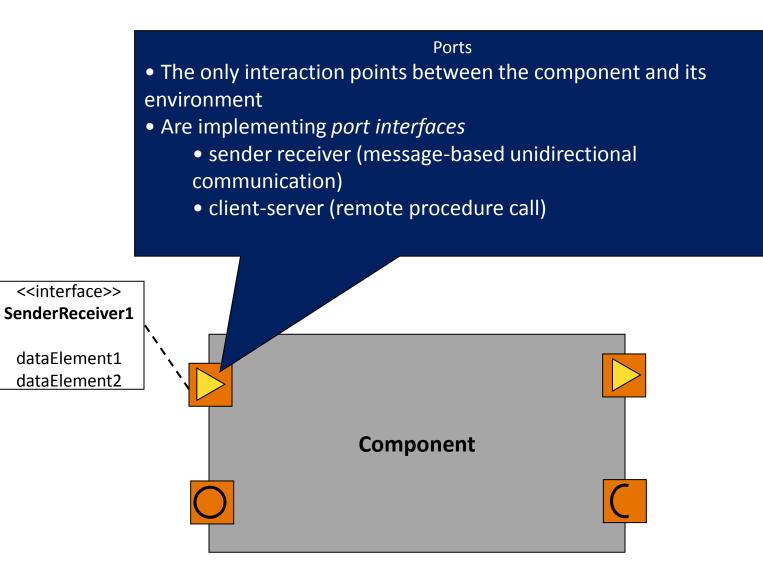

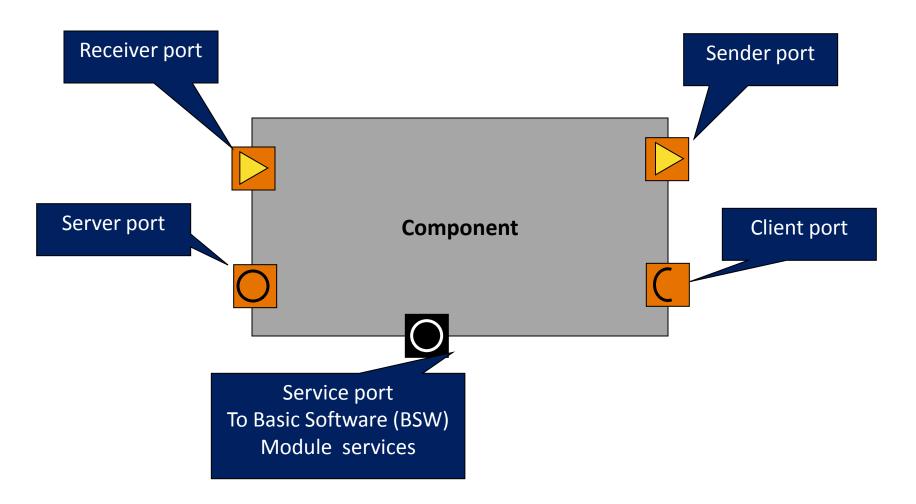

#### Component-based approach – port notation

#### Component interconnection – the Virtual Functional Bus

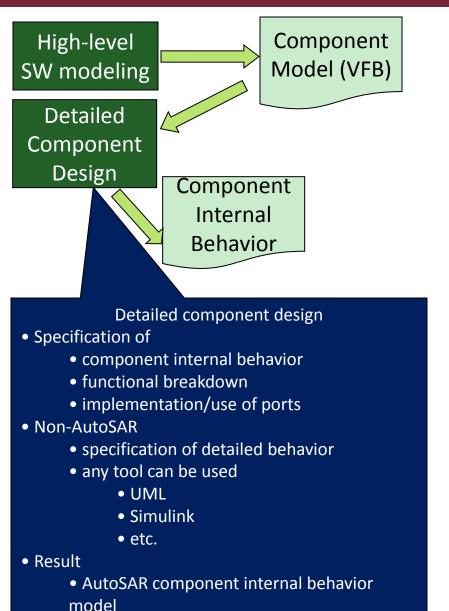

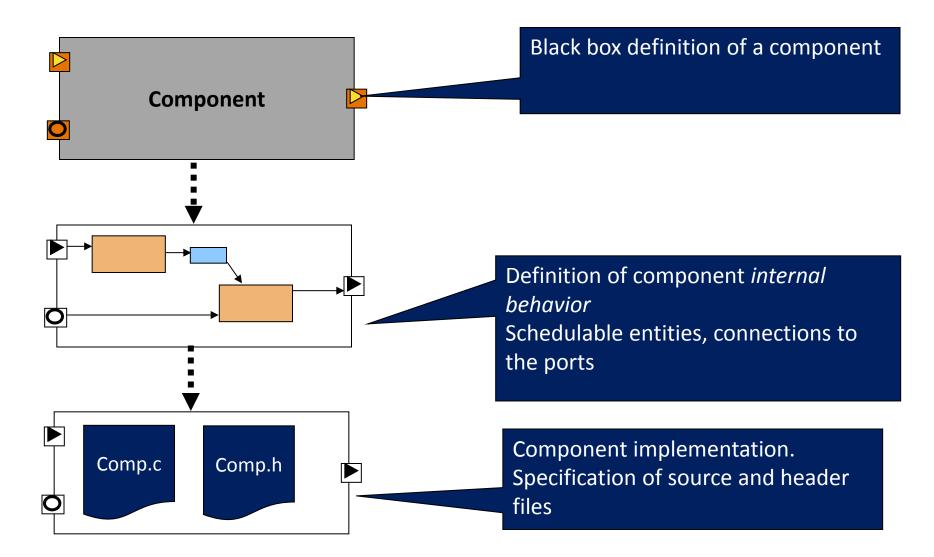

## Software Components

- On high-level, atomic components are black boxes

- Detailed design "looks into" these black boxes

- Main goals

- Detail the behavior to get schedulable entities

- Specify the semantics of port handling

- Specify any service needs

- Specify any RAM, nvRam needs

#### Refinement of a component

## Component internal behavior

- Specification of the internals of an atomic SWC

- Schedulable elements

Called: runnable entities

- Connection of ports

- Port semantics

- Port API options

- Inter-runnable communication

- Runnable activation and events

#### Component internal behavior – runnable entities

- Smallest code-fragments considered by RTE

- Subject to scheduling by the OS

- Abstraction of a schedulable function

- Communicates

- Using the SWC ports

- Using inter-runnable communication facilities

- Is activated by

- o An RTE event

- Communication-related event

- Timing event

## Summary of AUTOSAR

#### AUTOSAR defines

- A component-oriented system design approach

- Domain specific modeling language

- A high level design process

- Standard middleware (basic software) stack

- Standard interfaces

- Standard configuration descriptors

- AUTOSAR compliant ECU software

- Includes several BSW and application components

- RTE provides the integration (glue) between these

- Configuration and glue code is mostly auto-generated

Modeling IT infrastructure using ArchiMate

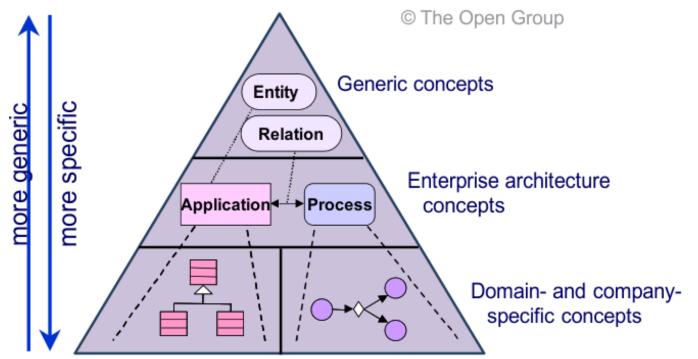

## IT system and infrastructure

Challenge: find a modeling language that is not too general neither too specific for a given domain

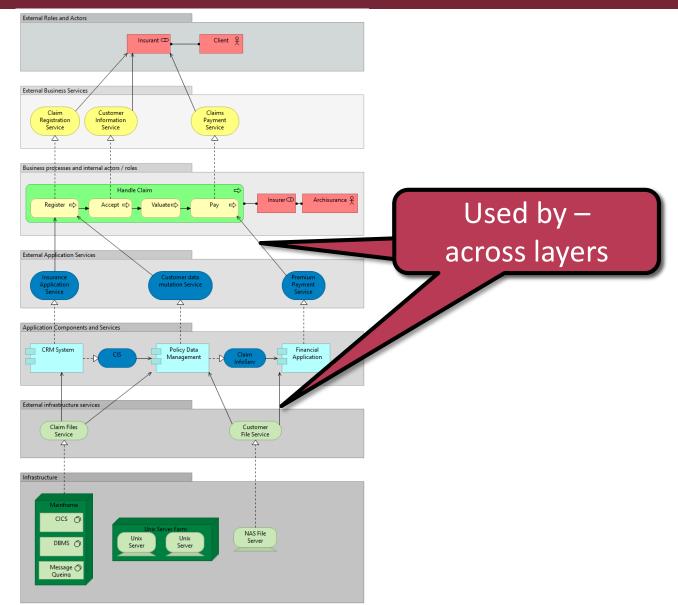

Applies multi-level allocation

# ArchiMate – infrastructure modeling

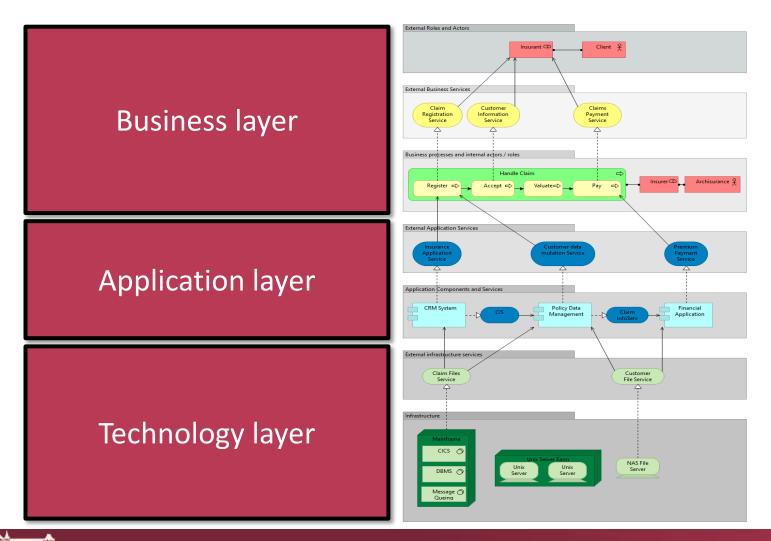

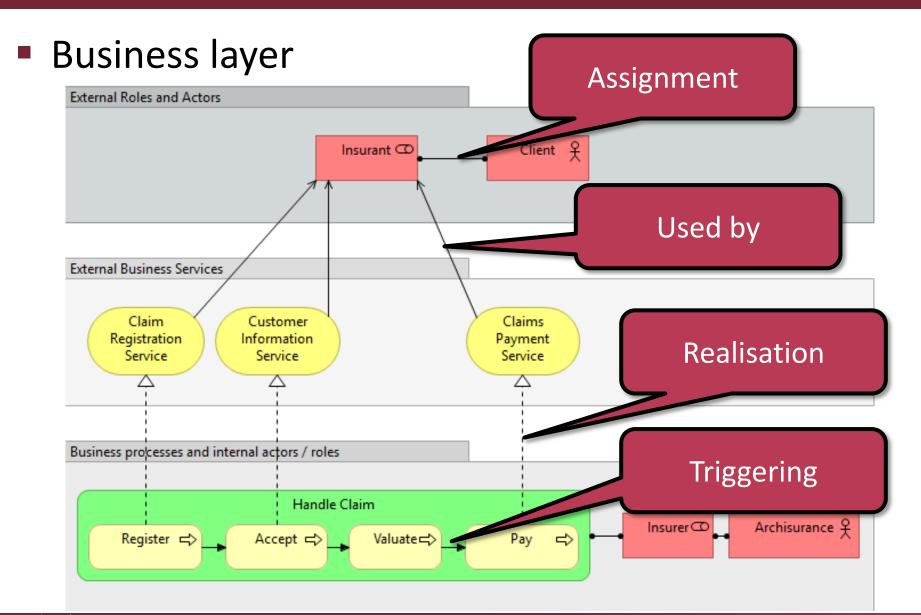

- The ArchiMate language defines three main layers

- The Business Layer offers products and services to external customers, which are realized in the organization by business processes performed by business actors.

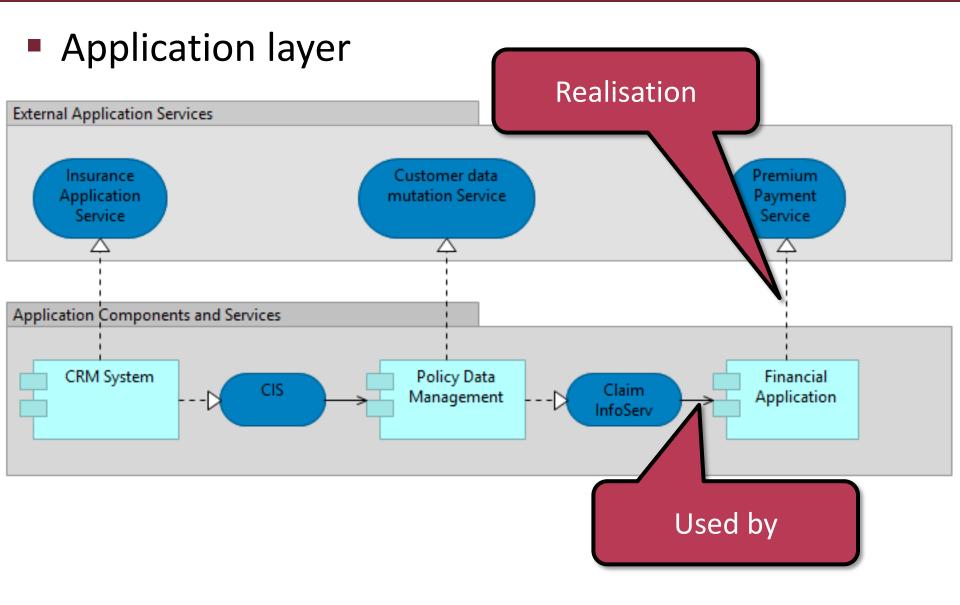

- The Application Layer supports the business layer with application services which are realized by (software) applications.

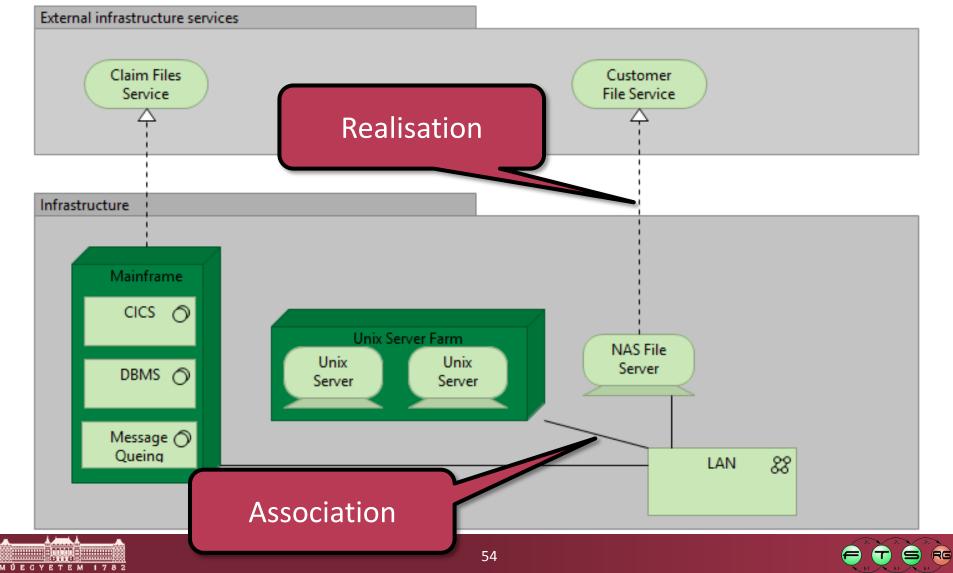

- The *Technology Layer* offers infrastructure services (e.g., processing, storage, and communication services) needed to run applications, realized by computer and communication hardware and system software.

### ArchiMate example – big picture

An example of a fictional Insurance company.

#### ArchiMate example: fictional Insurance company

м и в с у в т в м

#### ArchiMate example: fictional Insurance company

MÚEGYETEM

#### ArchiMate example: fictional Insurance company

#### Technology layer

#### ArchiMate example – big picture

MÚEGYETEM 1782

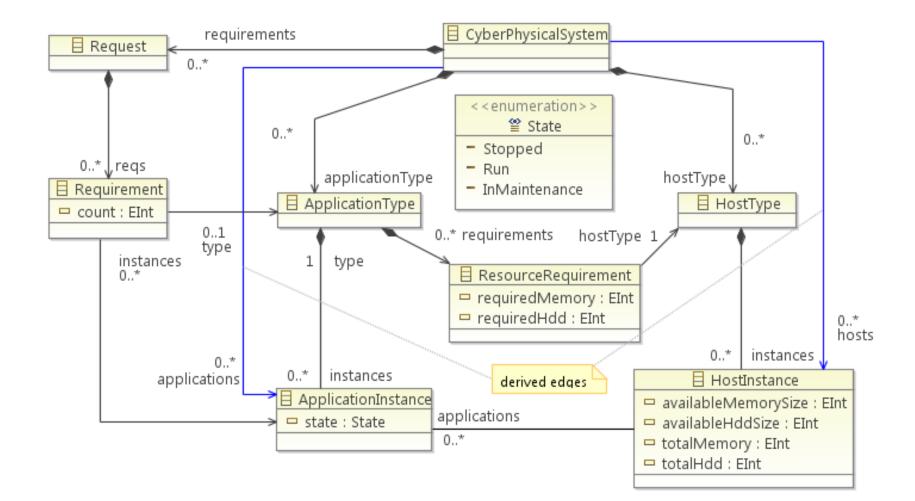

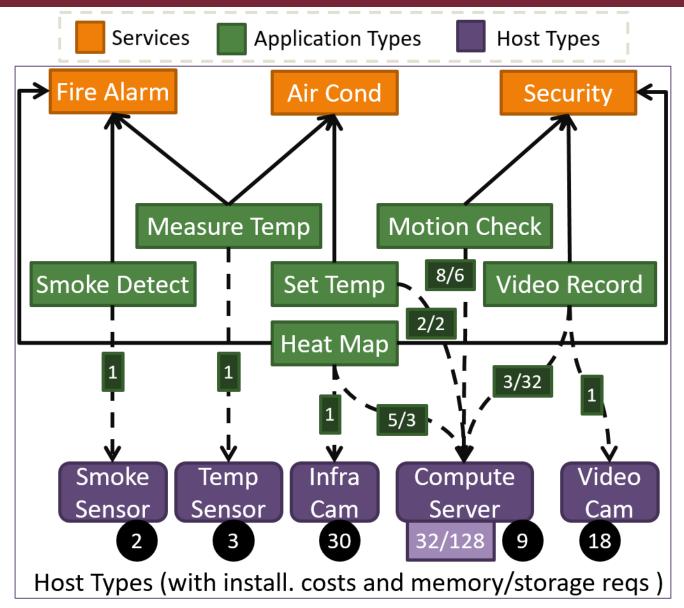

# Motivating example: Smart Building

- Reconfiguration of supervising cyber-physical systems (CPS)

- Offices to rent with highly configurable services

- Services to deploy on both embedded and virtual computational units

- Requests may change over time

Certain faulty devices may no longer function

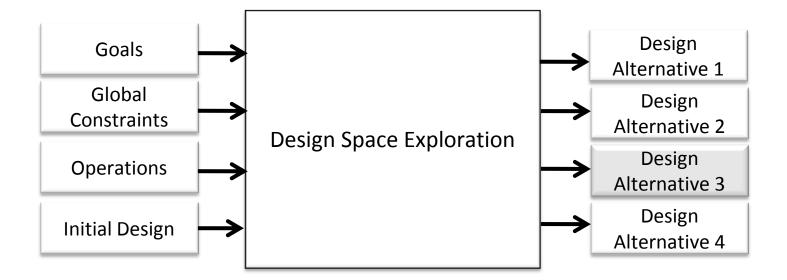

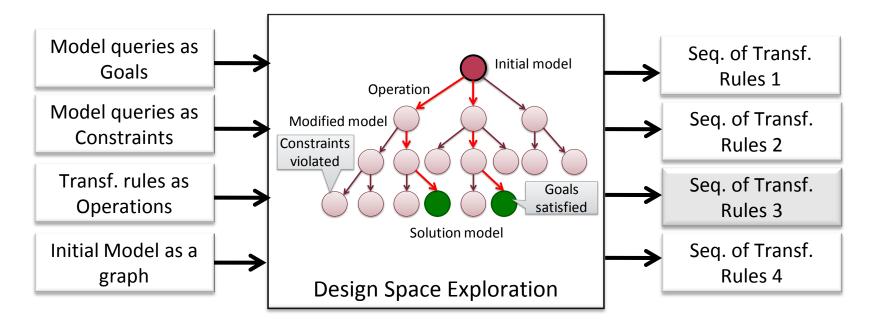

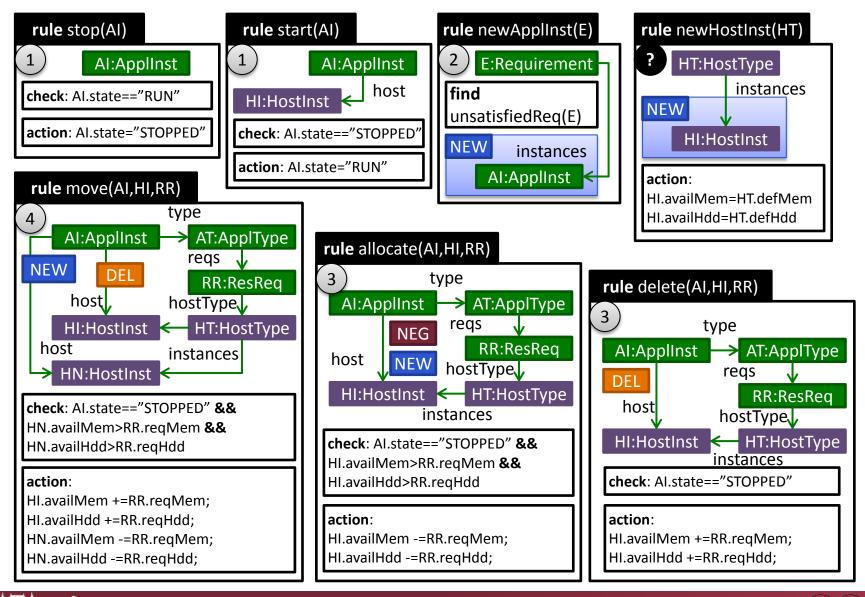

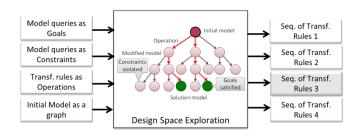

# Design Space Exploration (DSE)

- Special state space exploration

- Potentially infinite state space

- cannot put upper bound on the number of model elements used in a design candidate (elements are created and deleted during exploration).

# **Rule-based Design Space Exploration**

- Objectives : complex model metrics calculated by model queries

- Cost calculations may depend on the seq. of transf. rules

- Multiple objectives

## Motivating example: Smart Building

MÚEGYETEM 1782

## Motivating example: Smart Building

м Ú Е С Ү Е Т Е М

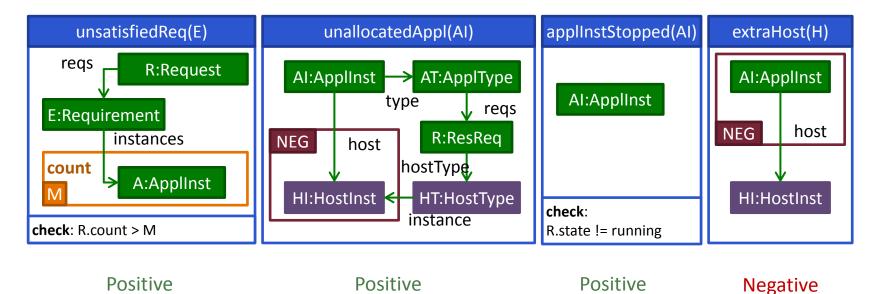

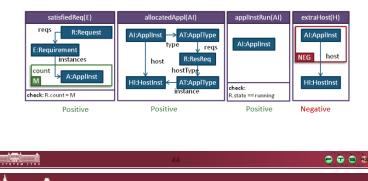

### Smart building: constraints

#### Constraints

#### Graph patterns to search for with model queries

#### For smart buildings

Constraints define valid or invalid configurations

## Smart building: constraints con't

Constraints

r1

<u>e1:Re</u> count instances

h1

Constraint fulfillment

$$ConstFulfillment(M) = \sum_{\forall p \in P} w_p \times matches(p, M)$$

$$Positive \text{ for well-formedness constraints}$$

$$Negative \text{ for ill-formedness constraints}$$

$$Negative \text{ for ill-formedness constraints}$$

$$Request$$

$$reqs$$

$$allocatedAppl 0 \quad 3 \quad 0$$

$$applInstRun \quad 0 \quad 4 \quad 0$$

$$extraHost \quad 1 \quad -1 \quad -1$$

$$HostInst$$

$$M = 1$$

## Smart building: rules

MÚEGYETEM 1782

#### Smart Building: configuration model Services and Requests

| Package | Services   | Appl Types                   |

|---------|------------|------------------------------|

| Basic   | Fire Alarm | Smoke Detect<br>MeasureTemp  |

| Comfort | + Air Cond | + SetTemp                    |

| Secure  | + Security | +MotionCheck<br>+VideoRecord |

| Max     |            | +HeatMap                     |

(a) Services

| R | Packages                | AppInst                                  | HostInst                           |

|---|-------------------------|------------------------------------------|------------------------------------|

| 1 | Comfort (2)<br>Basic(1) | 3xSD, 2xMT,<br>2xST                      | 3xSS,6xTS,<br>2xCS,                |

| 2 | Max (2)                 | 2xSD, 6xMT,<br>2xST, 2xMC,<br>2xVR, 2xHM | 2xSS,6xTS,<br>8xCS, 2xIC,<br>2xVC, |

(b) Two examples on company requests

#### Summary

#### Smart building: constraints

Constraints

MÚEGYETEM 1782

- Graph patterns to search for with model queries

- For smart buildings

- Constraints define valid or invalid configurations

#### High-level design process

#### **Rule-based Design Space Exploration**

- Objectives : complex model metrics calculated by model queries

- Cost calculations may depend on the seq. of transf. rules

0 0 0 0

RG

Multiple objectives

MÜECYETEM 17

## References

- http://www.ptidej.net/courses/log3410/fall11/Lectur es/Article\_6.pdf

- https://hal.archives-ouvertes.fr/hal-00110453/document

- http://pubs.opengroup.org/architecture/archimate2doc/toc.html

- <u>https://ocw.mit.edu/courses/aeronautics-and-astronautics/16-885j-aircraft-systems-engineering-fall-2005/readings/sefguide\_01\_01.pdf</u>

- http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumb er=1675654