# Meltdown: Modeling a vulnerability with timed automata

**Kristóf Marussy**

Budapest University of Technology and Economics Fault Tolerant Systems Research Group

### Meltdown and Spectre

- Critical vulnerabilities

in modern CPU architectures

Break kernel isolation of processes

Exploitation possible from JavaScript?

- Meltdown

- Unprivileged read of kernel memory

- Exploits speculative execution

- Spectre (Variants 1 and 2)

- Bounds check bypass

- Branch target injection

https://meltdownattack.com/

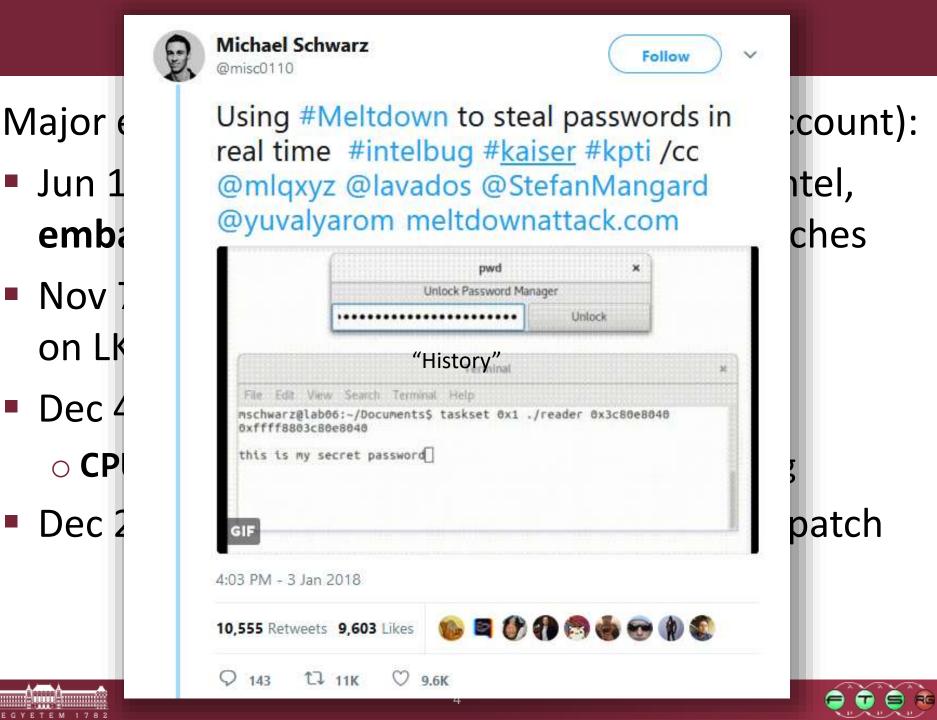

### "History"

Major events (but probably not a complete account):

- Jun 1, 2017 Google Project Zero notifies Intel, embargo to allow OS vendors to deploy patches

- Nov 7–27, 2017 KAISER patch series on LKML (Linux Kernel Mailing List)

- Dec 4, 2017 kpti patch on LKLM

CPU\_BUG\_INSECURE everyone is speculating

- Dec 27, 2017 do not enable pti on AMD patch

### "History"

Major events (but probably not a complete account):

- Jun 1, 2017 Google Project Zero notifies Intel, embargo to allow OS vendors to deploy patches

- Nov 7–27, 2017 KAISER patch series on LKML (Linux Kernel K

- Dec 4, 2017 kpti pat

OCPU\_BUG\_INSECURE -

Several other vulnerabilities were discovered since then using the same approach

- Dec 27, 2017 do not enable per ou m

- Jan 3, 2018 Tweet by Michael Schwarz, paper by University of Graz and Project Zero on arXiv

### References

- Moritz Lipp, Michael Schwarz, Daniel Gruss, Thomas Prescher, Werner Haas, Stefan Mangard, Paul Kocher, Daniel Genkin, Yuval Yarom, Mike Hamburg (2018).

*Meltdown*. arXiv:1801.01207

- Paul Kocher, Daniel Genkin, Daniel Gruss, Werner Haas, Mike Hamburg, Moritz Lipp, Stefan Mangard, Thomas Prescher, Michael Schwarz, Yuval Yarom (2018). Spectre Attacks: Exploiting Speculative Execution. arXiv:1801.01203

- Jann Horn, Project Zero (2018). Reading privileged memory with a side-channel. [Online] URL: <u>https://googleprojectzero.blogspot.com/2018/01/reading-privileged-memory-with-side.html</u>

What are we modelling and why?

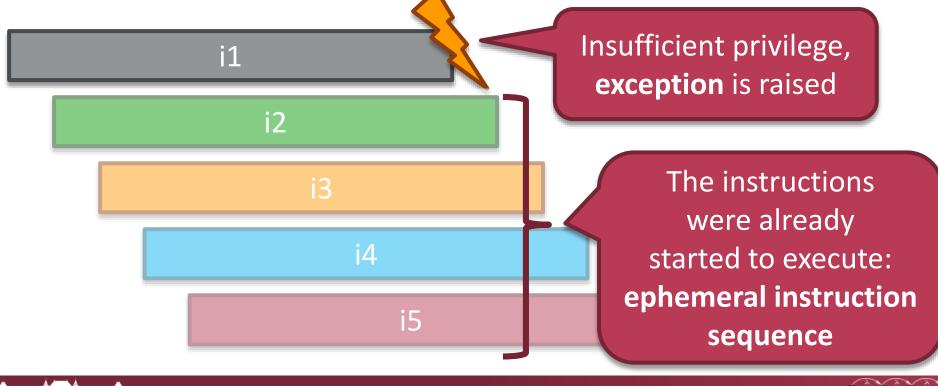

### Speculative execution

- Common technique in modern CPU architecture

- CPU starts executing instructions that may not be actually needed due to a jump or exception

- Speeds up pipelining and out-of-order execution

- Ephemeral instructions have no side effects observable in memory or the register file

- Even if we manage to circumvent privilege checks, we cannot exfiltrate the data – or can we?

Film: Steven Spielberg (2015). Bridge of Spies.

Film: Steven Spielberg (2015). Bridge of Spies.

- Ephemeral instructions have no side effects observable in memory or the register file

- Even if we manage to circumvent privilege checks, we cannot exfiltrate the data – or can we?

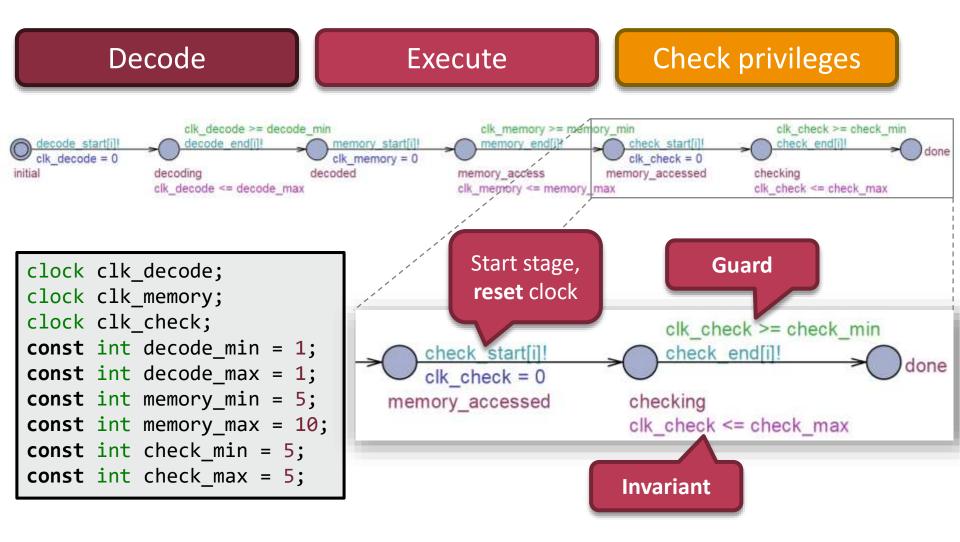

#### Solution: covert channel

- Undetectable (hidden) channel to information transfer

- Repurposes something originally not indented to transfer data

- In a CPU: microarchitectural covert channel

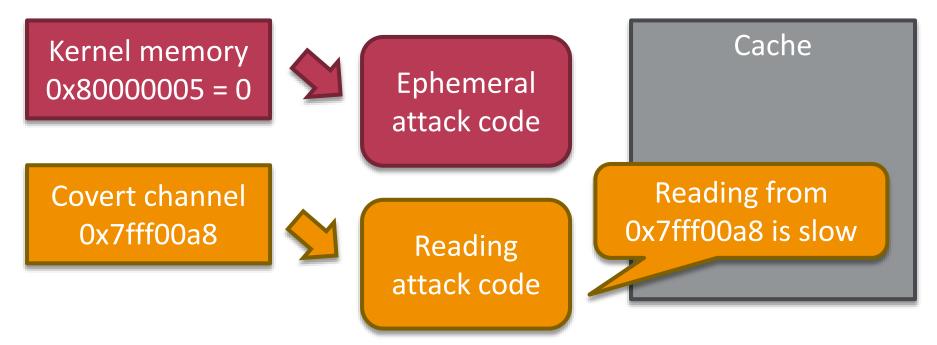

### Exfiltrate data via the cache

- Channel: pre-determined memory address

Initially not cached

- The exploiting code is allowed to read it

- Timing side channel: read data by measuring time

### Exfiltrate data via the cache

- Channel: pre-determined memory address

Initially not cached

- The exploiting code is allowed to read it

- Timing side channel: read data by measuring time

### Do we have enough time?

Challenge: Implement the exfiltration as an ephemeral instruction sequence

#### 6.4 Limitations on ARM and AMD

We also tried to reproduce the Meltdown bug on several ARM and AMD CPUs. However, we did not manage to successfully leak kernel memory with the attack described in Section 5, neither on ARM nor on AMD. The reasons for this can be manifold. First of all, our implementation might simply be too slow and a more optimized version might succeed. For instance, a more shallow out-of-order execution pipeline could tip the race condition towards against the data leakage. Similarly,

Let us explore the timing possibilities of a sufficiently short attack sequence with **timed automata**! certain features, e.g., no re-order plementation might not be able to for both ARM and AMD, the toy in Section 3 works reliably, indier execution generally occurs and al memory accesses are also per-

formed.

### SIMPLIFICATIONS, ABSTRACTIONS

Which part of the problem do we model?

### Simple processor model

We consider a 3-stage pipeline without out-of-order execution

- Each instruction goes through the states in this order, each state processes one instruction at a time sequentially

- We ignore any data dependencies between instructions

### Abstraction

- We do not model the internal state of the hardware (NOT hardware model checking)

- Abstraction of system clock ticks: Clock variables

- o How many clock ticks since the start of an activity?

- Specify execution times by invariants and guards

- Uppaal XTA formalism

- Abstraction of cache: flag variable (Boolean)

Is the memory location corresponding to the covert channel cached?

|             | Instruction             | Decoding           | Execution                | Check        |

|-------------|-------------------------|--------------------|--------------------------|--------------|

| 1.          | Read kernel memory      | 1 ticks            | 45-120 ticks             | 40-100 ticks |

| 2<br>N – 2. | Computation             | 1 ticks            | 10-15 ticks              | 5 ticks      |

| N - 1.      | Covert channel to cache | 1 ticks            | 45-120 ticks             | 10-25 ticks  |

|             | Execution proceeds      | from below after a | privilege exception      | ו:           |

| N.          | Read covert channel     | 1 ticks            | 45-120 or<br>15-30 ticks | 15-25 ticks  |

- Large execution times for illustration

- Length of the instruction sequence can be changed

- What is the maximum length that allows the exploit to work?

|             | Instruction         | Decoding        | Execution                 | Check        |

|-------------|---------------------|-----------------|---------------------------|--------------|

| 1.          | Read kernel memory  | 1 ticks         | 45-120 ticks              | 40-100 ticks |

| 2<br>N – 2. | Computation         | 1 ticks         | 10-15 ticks               | 5 ticks      |

| N - 1.      |                     | Read privileged |                           | 10-25 ticks  |

|             | Execution proce     | checking throws | exception ior             | ו:           |

| N.          | Read covert channel |                 | -15-120 or<br>15-30 ticks | 15-25 ticks  |

- Large execution times for illustration

- Length of the instruction sequence can be changed

- What is the maximum length that allows the exploit to work?

|             | Instruction                      | Deco | oding   | Execution                | Check        |

|-------------|----------------------------------|------|---------|--------------------------|--------------|

| 1.          | Read kernel memory               | 1    | ticks   | 45-120 ticks             | 40-100 ticks |

| 2<br>N – 2. | Computation                      | 1    | ticks   | 10-15 ticks              | 5 ticks      |

| N – 1.      | Соу                              |      | ticks   | 45-120 ticks             | 10-25 ticks  |

|             | Ephemeral instru                 | C    | after a | privilege exceptior      | 1:           |

| Ν.          | Re establishing t<br>covert chan |      | ticks   | 45-120 or<br>15-30 ticks | 15-25 ticks  |

- Large execution times for illustration

- Length of the instruction sequence can be changed

- What is the maximum length that allows the exploit to work?

|                                                     | Instruction               |                                                                  | Decoding | Execution    | Check        |

|-----------------------------------------------------|---------------------------|------------------------------------------------------------------|----------|--------------|--------------|

| 1.                                                  | Read kernel memory        |                                                                  | 1 ticks  | 45-120 ticks | 40-100 ticks |

| 2<br>N – 2.                                         | Computation               |                                                                  | 1 ticks  | 10-15 ticks  | 5 ticks      |

| N – 1.                                              | Covert channel to         | cache                                                            | 1 ticks  | 45-120 ticks | 10-25 ticks  |

| Execution procees slow after a privilege exception: |                           |                                                                  |          |              |              |

| N.                                                  | Read covert char          | Brings the covert channel<br>memory location <b>to the cache</b> |          |              | 15-25 ticks  |

|                                                     | ge executi<br>ngth of the | the <b>bit read</b> from the kerner                              |          |              | be changed   |

What is the maximum length that allows the exploit to work?

|             | Instruction            | Decoding                          | Exec          | ution          | Check        |

|-------------|------------------------|-----------------------------------|---------------|----------------|--------------|

| 1.          | Read kernel memory     |                                   |               | ) ticks        | 40-100 ticks |

| 2<br>N – 2. | Computation            | Read covert cha<br>contents after | -13           | ticks          | 5 ticks      |

| N – 1.      | Covert channel to cach | exception by <b>timing</b>        |               | ) ticks        | 10-25 ticks  |

|             | Execution proceed      | sy now arter a                    | privilege exc | ception        | :            |

| N.          | Read covert channel    | 1 ticks                           |               | 20 or<br>ticks | 15-25 ticks  |

- Large execution times f

- Length of the instruction

- What is the maximum letter that allows the exploit to work?

Depends on whether the covert channel memory location is **cached**

anged

How do we model the exploit?

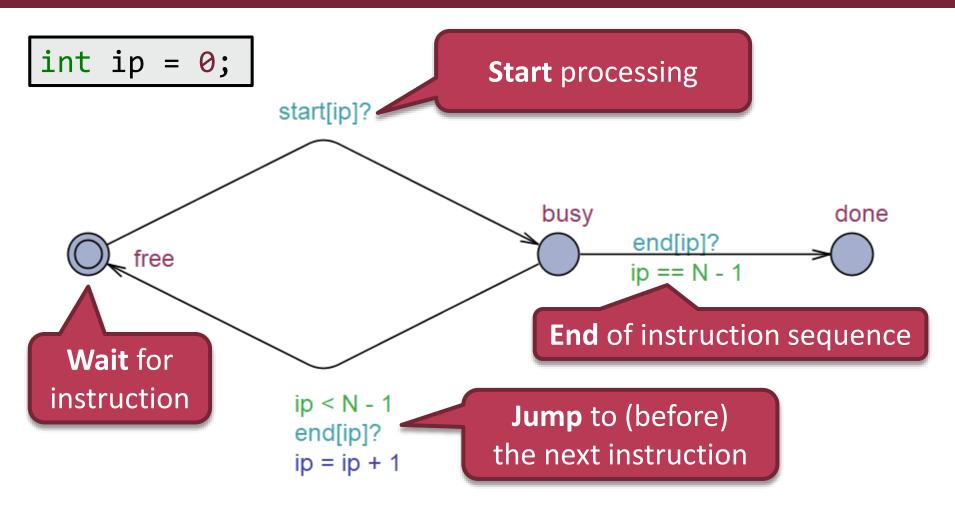

### Structure of the model

- 1. Timed automata for execution units

- 2. Timed automata for instructions

- **3.** Synchronization between execution units and instructions

- Customize instruction automata for individual behaviors of instructions

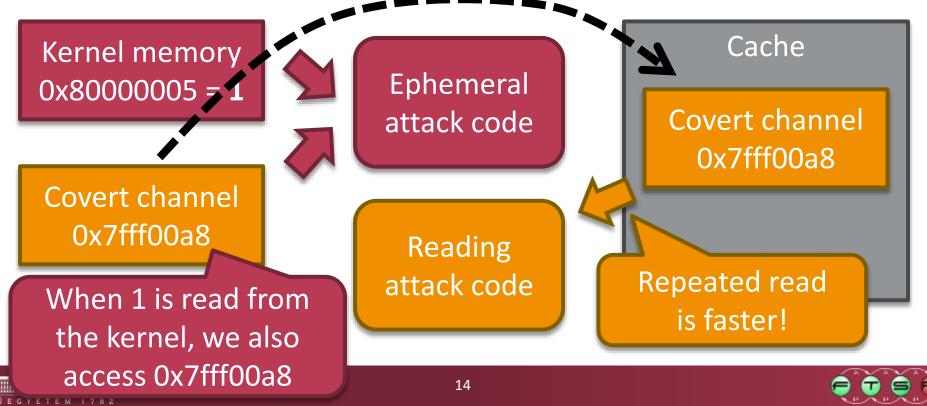

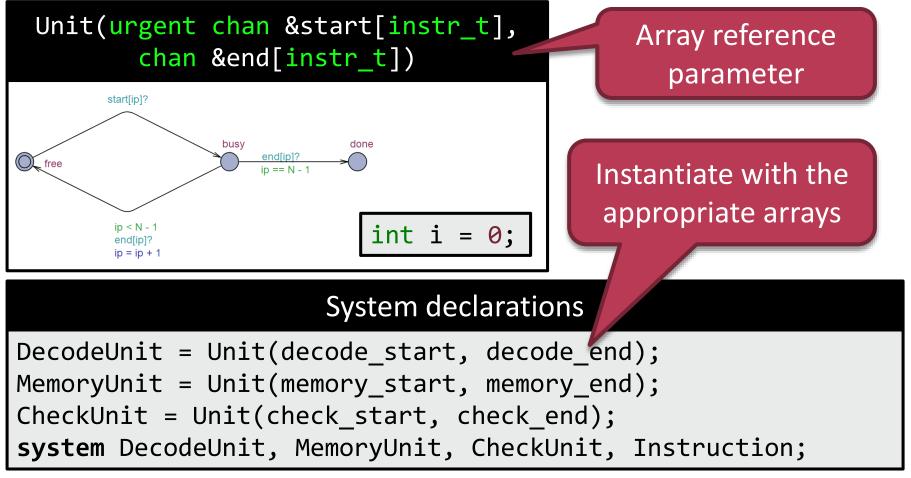

### Pipeline stage: Unit

#### Processing times are measured inside another automaton

### Instruction lifecycle: Instruction

- The pipeline stage (Unit) starts processing as soon as the current instruction can proceed

- Stages process instructions sequentially

- Instruction lifecycle (Instruction) determines processing times of pipeline stages

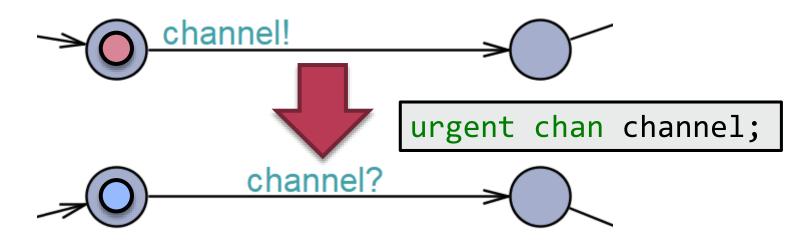

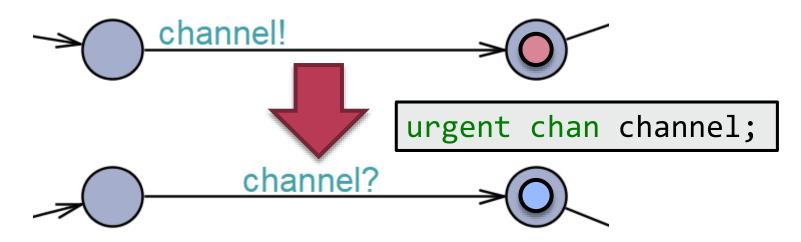

#### Urgent channel

## Immediately fires the state transition as soon as both the sender and receiver can proceed

Time cannot elapse in this state configuration of the automata

#### Urgent channel

#### Immediately fires the state transition as soon as both the sender and receiver can proceed

#### Urgent channel

#### Immediately fires the state transition as soon as both the sender and receiver can proceed

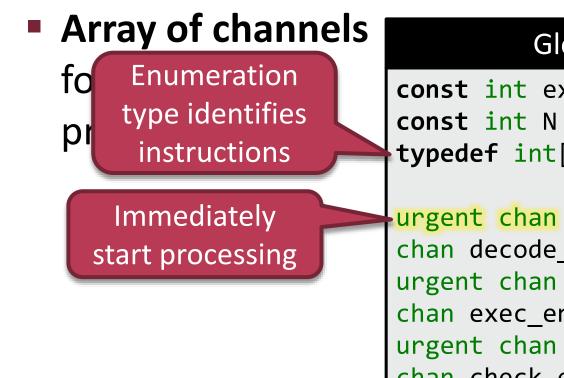

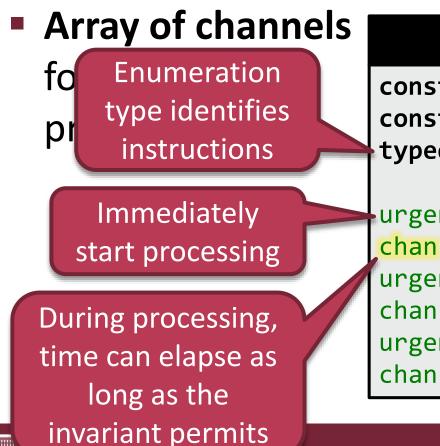

### Array of channels for sequential processing

#### **Global declarations**

```

const int exploit_size = 3;

const int N = exploit_size + 3;

typedef int[0,N - 1] instr_t;

```

```

urgent chan decode_start[instr_t];

chan decode_end[instr_t];

urgent chan exec_start[instr_t];

chan exec_end[instr_t];

urgent chan check_start[instr_t];

chan check_end[instr_t];

```

#### Urgent channel

## Immediately fires the state transition as soon as both the sender and receiver can proceed

#### Array of channels

fo Enumeration type identifies instructions

#### Global declarations

```

const int exploit_size = 3;

const int N = exploit_size + 3;

typedef int[0,N - 1] instr_t;

```

urgent chan decode\_start[instr\_t]; chan decode\_end[instr\_t]; urgent chan exec\_start[instr\_t]; chan exec\_end[instr\_t]; urgent chan check\_start[instr\_t]; chan check\_end[instr\_t];

#### Urgent channel

## Immediately fires the state transition as soon as both the sender and receiver can proceed

#### **Global declarations**

```

const int exploit_size = 3;

const int N = exploit_size + 3;

typedef int[0,N - 1] instr_t;

```

urgent chan decode\_start[instr\_t]; chan decode\_end[instr\_t]; urgent chan exec\_start[instr\_t]; chan exec\_end[instr\_t]; urgent chan check\_start[instr\_t]; chan check\_end[instr\_t];

#### Urgent channel

#### Immediately fires the state transition as soon as both the sender and receiver can proceed

#### **Global declarations**

```

const int exploit_size = 3;

const int N = exploit_size + 3;

typedef int[0,N - 1] instr_t;

```

urgent chan decode\_start[instr\_t]; chan decode\_end[instr\_t]; urgent chan exec\_start[instr\_t]; chan exec\_end[instr\_t]; urgent chan check\_start[instr\_t]; chan check\_end[instr\_t];

Single Unit template for each pipeline state

Parameterized by channel array references

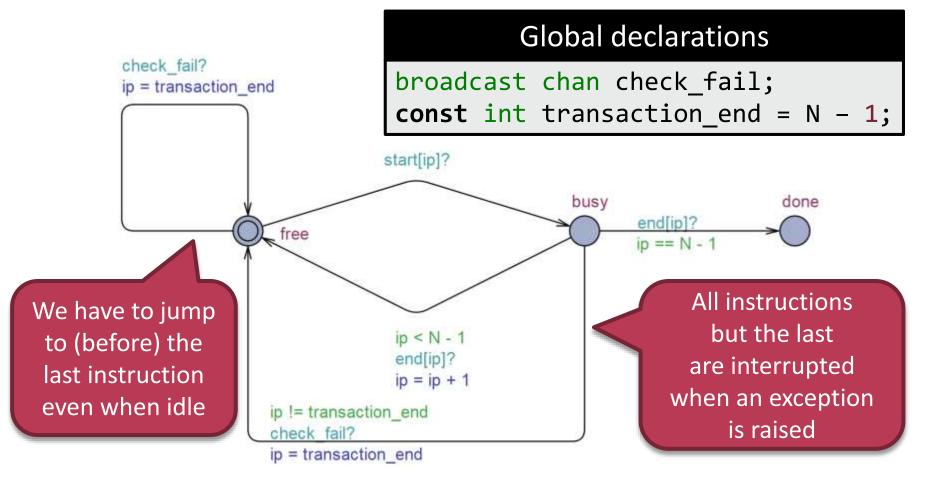

### Modelling exception handling

- Every pipeline stage should receive the exception

- Broadcast channels: arbitrarily many (≥0) receivers

### Modelling the attack code

| i          | Instruction                                         | Behavior                                                                                                                                                                   |  |  |  |

|------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0.         | ReadKernelInstruction                               | Fails privilege check and raises exception                                                                                                                                 |  |  |  |

| 1<br>N – 3 | Instruction                                         | Computations for establishing the covert channel in exploit_size instances of the template (configurable as a global constant), the <b>index</b> i is a template parameter |  |  |  |

| N – 2      | WriteSCInstruction                                  | Cache the covert channel memory location if 1 is read                                                                                                                      |  |  |  |

|            | Ide ugrik a végrehajtás kivétel keletkezése esetén: |                                                                                                                                                                            |  |  |  |

| N - 1      | ReadSCInstruction                                   | Execution time depends on whether the covert channel memory location was cached                                                                                            |  |  |  |

We create multiple copies

of the original Instruction template

OMODIFIED TO MODIFIED TO

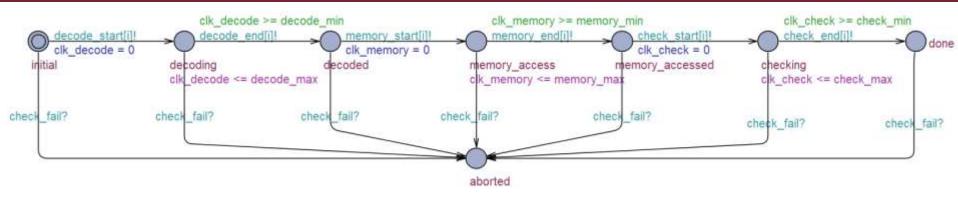

### ReadKernelInstruction

#### Checking raises an exception

### Instruction(exploit\_t i)

- 1st, ..., (N 3)th instructions: calculation

- Move to location aborted upon exception

- exploit\_t i parameter of enumerated type

- Instantiate as system Instruction;

for all possible values of exploit\_t

**Global declarations**

typedef int[1,exploit\_size] exploit\_t;

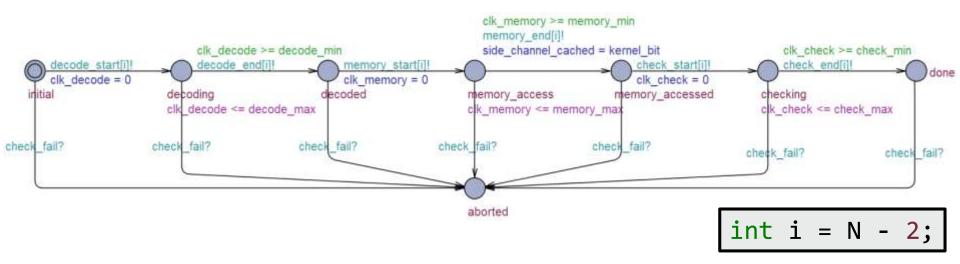

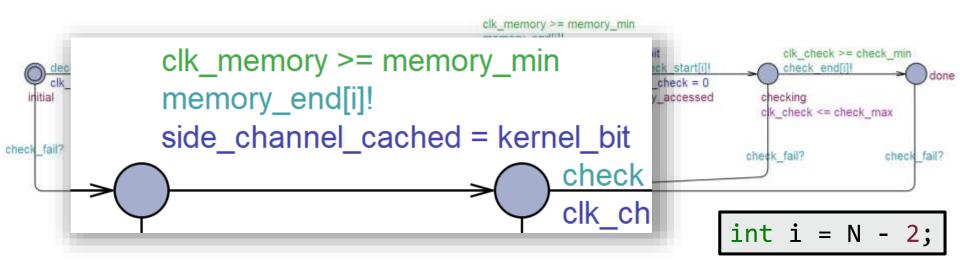

### WriteSCInstruction

Caches the covert channel memory location if the bit 1 is read from kernel memory

| Global declarations                                                        |

|----------------------------------------------------------------------------|

| <pre>const bool kernel_bit = true; bool side_channel_cached = false;</pre> |

### WriteSCInstruction

Caches the covert channel memory location if the bit 1 is read from kernel memory

| Global declarations                                                        |

|----------------------------------------------------------------------------|

| <pre>const bool kernel_bit = true; bool side_channel_cached = false;</pre> |

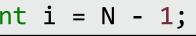

### ReadSCInstruction

- Execution time depends on covert channel state

- Will not be interrupted by exception <u>int i</u>

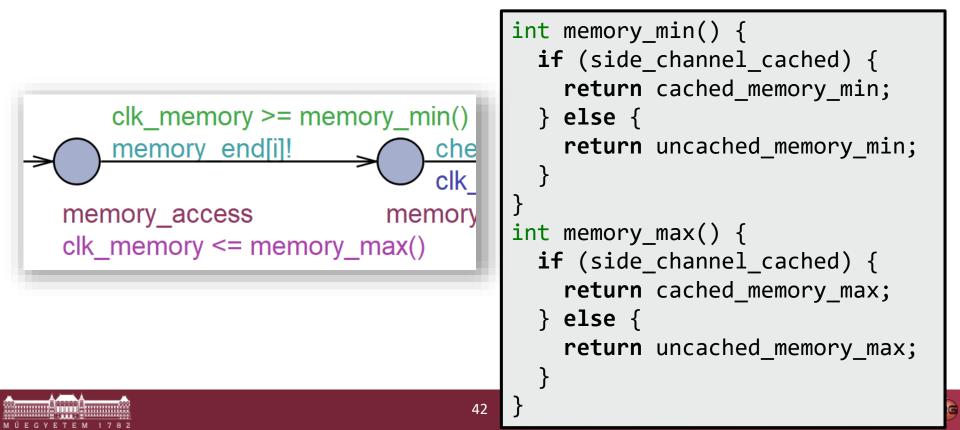

### Putting it together

#### Timing values are global constants

Instantiate processes in the system declaration section

#### **Global declarations**

```

const int decode_min = 1;

const int decode_max = 1;

const int uncached_memory_min = 45;

const int uncached_memory_max = 120;

const int cached_memory_max = 120;

const int cached_memory_min = 15;

const int cached_memory_max = 30;

const int kernel_check_min = 40;

const int kernel_check_min = 40;

const int kernel_check_max = 100;

const int user_check_min = 10;

const int user_check_max = 25;

```

#### System declarations

DecodeUnit = Unit(decode\_start, decode\_end); MemoryUnit = Unit(memory\_start, memory\_end); CheckUnit = Unit(check\_start, check\_end); system DecodeUnit, MemoryUnit, CheckUnit, ReadKernelInstruction, Instruction, WriteSCInstruction, ReadSCInstruction;

### **DEMO** Timed automata model checking

- Is the instruction before the last (WriteSCInstruction) never fully processed?

- Can the last instruction (ReadSCInstruction) always read kernel memory via the covert channel?

- At least how many clock cycles does running the exploit take, if ReadSCInstruction is executed and...

o ...kernel memory contains a 1 bit?

...kernel memory contains a 0 bit?

How many calculation instructions (exploit\_size) can we use while still ensuring a successful attack?