# SysML Miscellaneous Grab Bag

Systems Engineering BSc Course

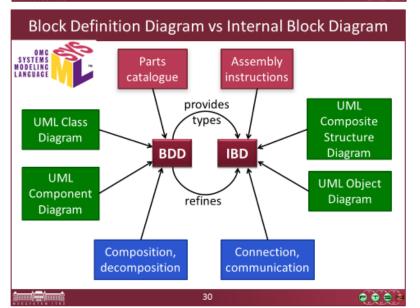

# Modeling of logical and physical data

Using block definition diagrams

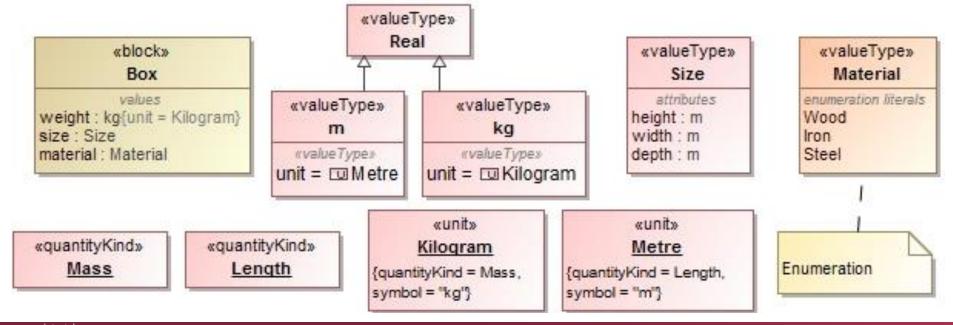

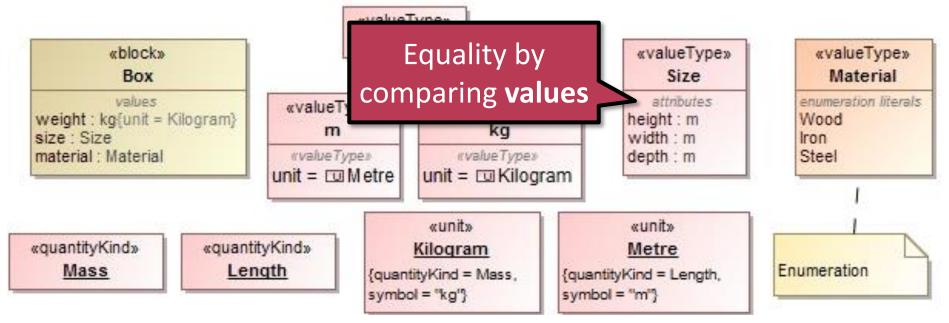

# Value type (Data type)

- Primitives: Boolean, String, Complex, etc.

- Can have Unit and/or QuantityKind (formerly dimension)

- QuantityKind: Length, Energy, Time, etc.

- Unit: meter, inch, Watt, secundum, etc.

- Has a QuantityKind

# Value type (Data type)

- Primitives: Boolean, String, Complex, etc.

- Can have Unit and/or QuantityKind (formerly dimension)

- QuantityKind: Length, Energy, Time, etc.

- Unit: meter, inch, Watt, secundum, etc.

- Has a QuantityKind

#### Data of a block

- Blocks can have attributes and/or values

- Value given by / restricted by

- Definition (bdd)

- e.g. in a specialized block (motorized = "true")

- Use (ibd)

- Runtime

- The value may change over time

#### Signal, Block

- A signal defines a message that can be sent and received by a block.

- Has a set of attributes

- Used by interfaces

«signal»

#### **TrainCurrentSpeed**

attributes

+currentSpeed: uint32

+direction: TrainDirectionValue

# Well-formedness constraints

#### Well-formedness constraints

- Describes additional constraints that should be satisfied on every instance

- Structural constraint

- A turnout sensor should be connected to exactly one zone controller

- Value constraint

- The operator should be at least 175 cm tall

- Components should have a unique name

- Behavioral constraint

- CPU should receive 12V +- 1V electricity

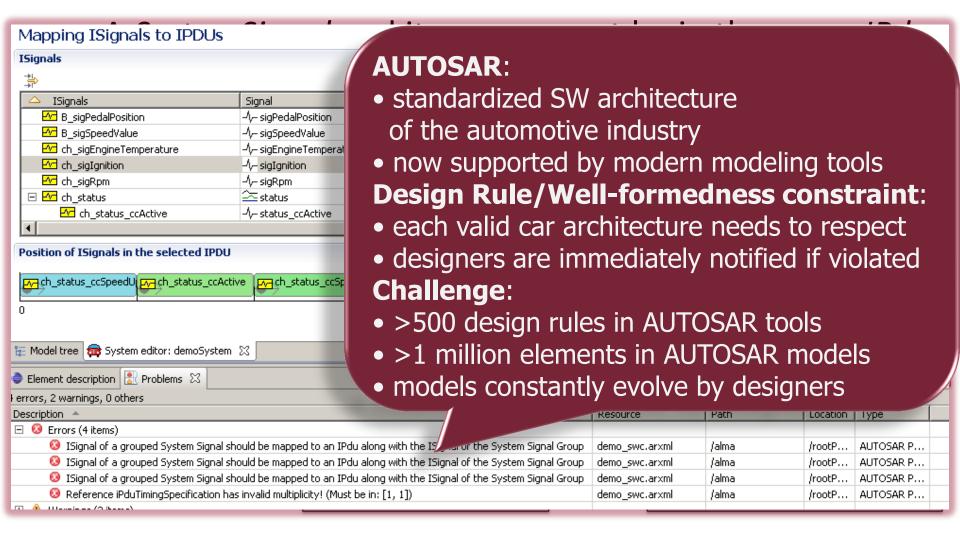

### Motivation: Early validation of design rules

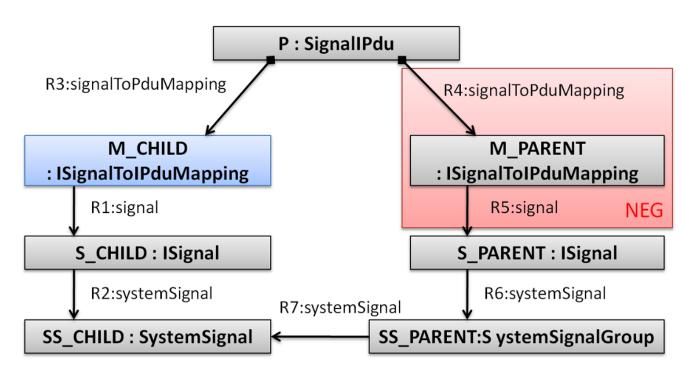

#### **SystemSignalGroup** design rule (from AUTOSAR)

- A SystemSignal and its group must be in the same IPdu

- Challenge: find violations quickly in large models

- New difficulties

- reverse navigation

- complex manual solution

# Motivation: Early validation of design rules

#### SystemSignalGroup design rule (from AUTOSAR)

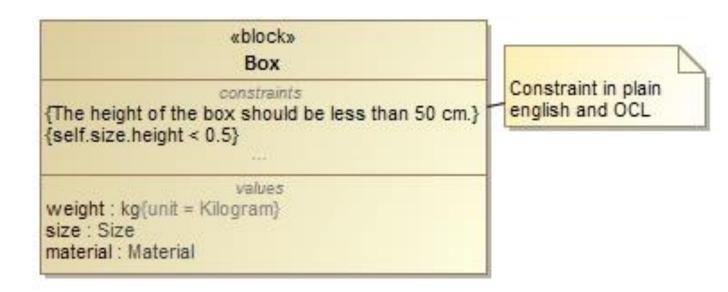

#### SysML Constraints

- Different semantics can be used

- o plain english vs formal languages (OCL, Javascript, etc.)

- formal language can be used for automatic validation

- Can also be defined as a separate block with <<constraint>> stereotype

#### SysML Constraints

Different comantice can be used Don't confuse with nguages (OCL, Javascript, etc.) SysML Parametrics Diagram! used for automatic validation Constraints are given by the designers arate block with Parametrics diagram considers pe the behaviour of nature (will cover later) block» Box Constraint in plain constraints. english and OCL {The height of the box should be less than 50 cm.} {self.size.height < 0.5} values weight : kg(unit = Kilogram) size : Size

material: Material

#### OCL: an OMG Standard

- Object Constraint Language

- Declarative language for defining constraints

Unique name constraint defined by OCL:

```

o context Component inv:

Component.allInstances()->

forAll(c1, c2 |

c1 <> c2 implies c1.name <> c2.name)

```

#### **VIATRA**

- VIATRA is an open source Eclipse project

- Affiliated with the research group

- VIATRA Query Language

- Graph pattern matching

- Can evaluate queries incrementally upon changes

- Unique name constraint defined by VQL

```

opattern nameCollision(c1, c2) {

Component.name(c1,name1);

Component.name(c2,name2);

c1 != c2;

name1 == name2;}

```

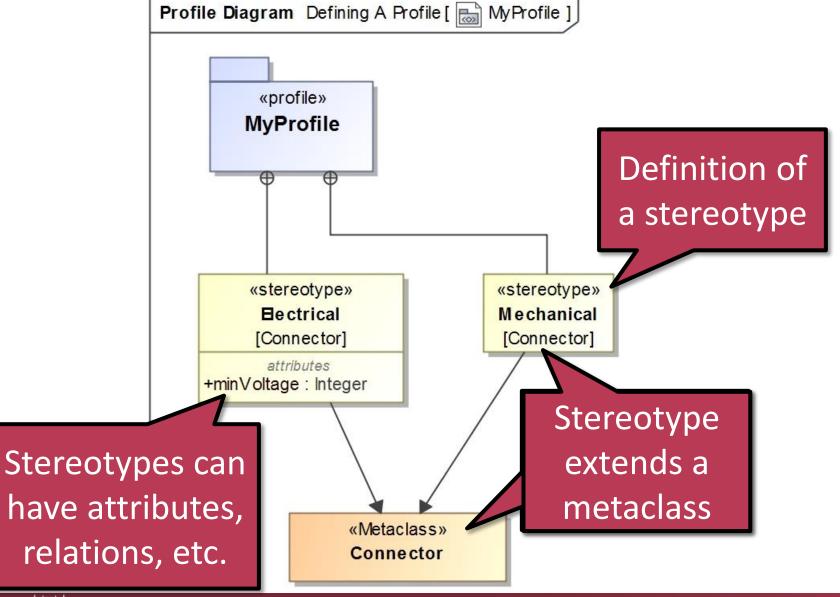

#### **Profiles**

for extending UML/SysML

#### **UML** Profiles

- Profiles can be used to extend the UML/SysML language.

- Examples

- SysML is defined as a profile on a subset of UML.

- SYSMOD (a methodology for SysML) also defines a profile for SysML

- MARTE (which is an OMG standard) profile is used for modeling real-time and embedded applications.

- Tools usually support the creation of custom profiles.

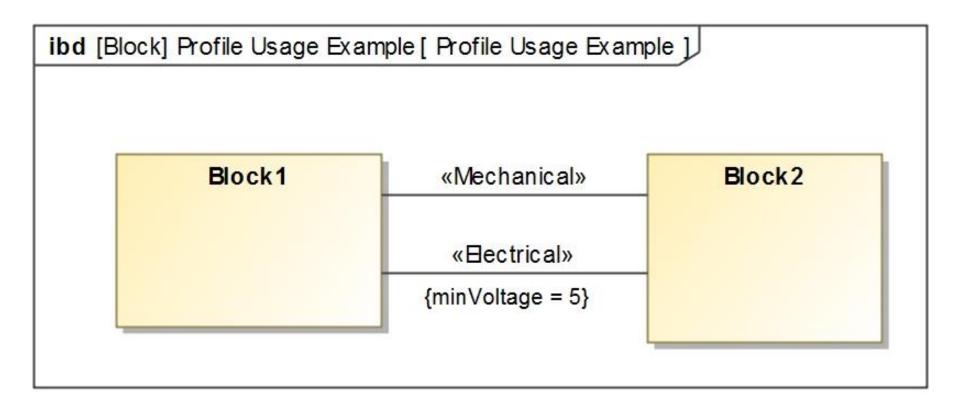

#### Defining a Profile

#### Using a Profile

A profile should be applied to the project to use

#### Summary

#### Top-down and bottom-up design Top-down: using decomposition When designing a subsystem, its goal is already Subsystems (2) There are no working parts during development ® Problems, needs of subsystems revealed late Bottom-up: using composition Subsytems of subsystems © Subsystems can be tested one-by-one System There are always some working parts during development Subsystems B Exact roles of the subsystems are revealed late. (Not only in structural modeling...) Meet-in-the-middle approach Iterative approaches

#### **Ports** What is a port? o Interaction points with external entities limiting and differentiating the possible connection types /api/InventoryItem CreateInventorvitemComm Creates a new inventory REST API: and (input) item GET /api/InventoryItem InventoryItemListDataColle Returns all items ction (output) PUT /api/InventoryItem/(id) RenameInventoryItemCom Renames an item ---

#### Well-formedness constraints

- Describes additional constraints that should be satisfied on every instance

- Structural constraint

- A turnout sensor should be connected to exactly one zone controller

- Value constraint

- o The operator should be at least 175 cm tall

- o Components should have a unique name

- Behavioral constraint

- o CPU should receive 12V +- 1V electricity

- -